hBPF + LiteETH for real network packet processing

This project shows how to process real network packets with hBPF. It uses a Digilent Arty-S7 with a MultiNet expansion board.

The Arty-S7 does not have Ethernet out of the box. Therefore Ethernet for the Arty-S7 was provided using MultiNet.

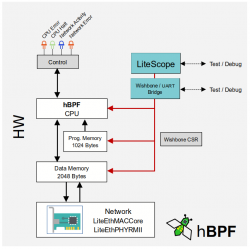

The project instantiates a hBPF CPU and connects it to a LiteEth low level LiteEthMACCore to receive network packets. Some CPU status signals are connected to LED’s. A serial Wishbone Bridge and LiteScope Debugger are used for debugging.

[Read more…]

Introducing hBPF - an eBPF implementation for FPGAs.

This project was started beginning of 2021 as an experiment of how fast and how far you can get, with using alternate hardware description languages (compared to the classic ‘V’ languages VHDL and Verilog), most of the time open-source tools (compared to expensive, commercial toolchains) and cheap development boards (e.g Arty-S7).

It implements an eBPF CPU using LiteX/Migen, a Python3 based SoC builder and Hardware Definition language (HDL).

[Read more…]

Thursday, September 10, 2020

PyAgentX3 is a pure Python3 implementation of the AgentX protocol (RFC 2741).

It will allow to extend an SNMP agent (e.g Net-SNMP snmpd) by writing AgentX subagents without modifying the original SNMP agent.

RFC 2741: Agent Extensibility (AgentX) Protocol

Code and samples can be found on github.

It features:

- Open a session with AgentX master, e.g. net-snmpd snmpd, and register a new session.

- Send Ping request.

- Register multiple MIB regions.

- Multiple MIB update classes with custom frequency for each.

- Support snmpset operations.

- Reconnect/Retry to master, in case the master restarted.

- Support for SNMPv2 traps.

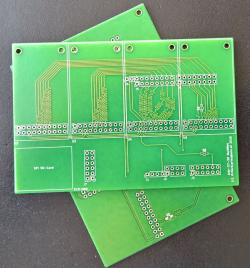

The prototype of my simple FPGA based SoC with multiple Ethernet interfaces worked so well that I decided to create a PCB for it and increase the number of network interfaces from two to four. It also includes a special PMOD connector for a SD-Card to boot a firmware or Linux from. Also two of the Arty’s four existing PMODs are also still available for extensions. PMOD-C and PMOD-D are no longer available as their pins are used for some of the Ethernet PHY modules.

Due to I/O limitations the Seven Segment Display was removed from the original design.

[Read more…]

In my day to day business I work with Software Defined Networking (SDN) a lot. Especially with Open-Flow, Open-vSwitch and some commercial products.

Most of the time the projects are not “normal” ones where these techniques are used in larger scenarios like enterprise or data-center networks. Instead I use them on the other side of the scale in embedded environments for example to develop Space based satellite routers.

At the time of this writing we now have almost eight weeks lock-down due to the SARS-CoV-2 pandemic. This means no travel time to my office and instead working from home. So this spare time must be filled with some experiments. Unfortunately at home I don’t have the resources I normally have at my workplace. So no fancy, multi k-euro development boards and tools. Wanting an embedded system with at least two Ethernet interfaces I looked around in my electronic junkyard and found some interesting components which might give a not so bad platform for some networking experiments. Especially low level Ethernet packet handling (filtering, modifying) is on of my interests. Maybe playing with P4, NetCope, or P4FPGA without spending a fortune.

[Read more…]